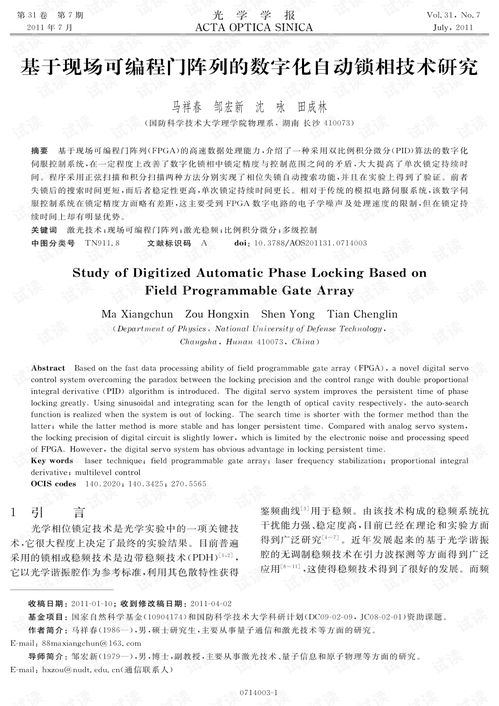

本文旨在探討基于現(xiàn)場(chǎng)可編程門陣列的數(shù)字化自動(dòng)鎖相技術(shù),分析其設(shè)計(jì)原理、系統(tǒng)架構(gòu)、實(shí)現(xiàn)方法及其在通信、測(cè)量、電力電子等領(lǐng)域的應(yīng)用優(yōu)勢(shì)與發(fā)展前景。

隨著數(shù)字信號(hào)處理技術(shù)的飛速發(fā)展,傳統(tǒng)的模擬鎖相環(huán)因其存在溫漂、元件老化、調(diào)試復(fù)雜等固有缺陷,已難以滿足現(xiàn)代高精度、高穩(wěn)定性電子系統(tǒng)的需求。數(shù)字化自動(dòng)鎖相技術(shù)應(yīng)運(yùn)而生,它利用數(shù)字電路或數(shù)字信號(hào)處理器實(shí)現(xiàn)對(duì)信號(hào)相位和頻率的精確跟蹤與同步。現(xiàn)場(chǎng)可編程門陣列作為一種高度靈活、可重構(gòu)的半導(dǎo)體器件,憑借其并行處理能力強(qiáng)、開(kāi)發(fā)周期短、易于實(shí)現(xiàn)復(fù)雜算法和系統(tǒng)集成等優(yōu)勢(shì),成為實(shí)現(xiàn)高性能數(shù)字化鎖相系統(tǒng)的理想硬件平臺(tái)。

一、數(shù)字化自動(dòng)鎖相技術(shù)的基本原理

數(shù)字化自動(dòng)鎖相環(huán)的核心功能模塊包括:數(shù)字鑒相器、數(shù)字環(huán)路濾波器和數(shù)字控制振蕩器。其工作原理與模擬鎖相環(huán)類似,但信號(hào)處理均在數(shù)字域完成。

- 數(shù)字鑒相器:負(fù)責(zé)比較輸入?yún)⒖夹盘?hào)與反饋信號(hào)的相位差,并將此差值轉(zhuǎn)換為數(shù)字誤差信號(hào)。常用算法包括過(guò)零檢測(cè)法、乘法鑒相法(如正交下變頻結(jié)合反正切運(yùn)算)等,能夠精確提取相位誤差。

- 數(shù)字環(huán)路濾波器:作為系統(tǒng)的控制核心,其作用是濾除鑒相器輸出中的高頻噪聲和干擾,并確定系統(tǒng)的動(dòng)態(tài)響應(yīng)特性(如鎖定速度、帶寬、穩(wěn)定性)。通常采用比例-積分結(jié)構(gòu),其參數(shù)可靈活配置以適應(yīng)不同應(yīng)用需求。

- 數(shù)字控制振蕩器:根據(jù)環(huán)路濾波器輸出的控制字,生成頻率和相位可精確調(diào)整的本地信號(hào)。數(shù)控振蕩器的實(shí)現(xiàn)方式多樣,如直接數(shù)字頻率合成技術(shù),它能產(chǎn)生高分辨率、高穩(wěn)定度的輸出信號(hào)。

二、基于FPGA的系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)

FPGA為實(shí)現(xiàn)上述數(shù)字化模塊提供了高效平臺(tái)。其設(shè)計(jì)流程主要包括算法建模、硬件描述語(yǔ)言編碼、功能仿真、綜合與布局布線、板級(jí)調(diào)試等步驟。

- 系統(tǒng)架構(gòu):典型的基于FPGA的數(shù)字化鎖相環(huán)系統(tǒng)通常包含高速模數(shù)轉(zhuǎn)換器、FPGA核心處理單元以及必要的存儲(chǔ)器與外設(shè)接口。ADC將模擬輸入信號(hào)數(shù)字化后送入FPGA處理。

- 模塊實(shí)現(xiàn):

- 鑒相器:可利用FPGA內(nèi)部的乘法器、查找表和狀態(tài)機(jī)資源高效實(shí)現(xiàn)。對(duì)于正交鑒相,可結(jié)合坐標(biāo)旋轉(zhuǎn)數(shù)字計(jì)算機(jī)算法進(jìn)行相位差計(jì)算。

- 環(huán)路濾波器:可采用流水線或并行結(jié)構(gòu)實(shí)現(xiàn)數(shù)字濾波器(如IIR或FIR濾波器),其系數(shù)可通過(guò)在線更新以適應(yīng)動(dòng)態(tài)變化。

- 數(shù)控振蕩器:利用FPGA查找表實(shí)現(xiàn)相位累加器和正弦/余弦波形查找表,是構(gòu)建高性能DDS的常用方法。

- 關(guān)鍵技術(shù):

- 并行處理與流水線:FPGA的并行架構(gòu)允許同時(shí)處理多個(gè)數(shù)據(jù)流,顯著提升系統(tǒng)處理速度和實(shí)時(shí)性。

- 資源優(yōu)化:通過(guò)合理設(shè)計(jì)數(shù)據(jù)位寬、采用時(shí)分復(fù)用或共享邏輯資源,在保證性能的同時(shí)優(yōu)化FPGA的邏輯和存儲(chǔ)資源消耗。

- 動(dòng)態(tài)重配置:部分FPGA支持動(dòng)態(tài)部分重配置,可在系統(tǒng)運(yùn)行中切換鎖相環(huán)參數(shù)或算法,實(shí)現(xiàn)多功能自適應(yīng)。

三、技術(shù)優(yōu)勢(shì)與應(yīng)用

基于FPGA的數(shù)字化自動(dòng)鎖相技術(shù)具有顯著優(yōu)勢(shì):

- 高精度與穩(wěn)定性:數(shù)字處理避免了模擬器件的漂移,算法精度僅受限于字長(zhǎng)和時(shí)鐘頻率,具有優(yōu)異的長(zhǎng)期穩(wěn)定性。

- 靈活性與可重構(gòu)性:鎖相環(huán)的環(huán)路帶寬、阻尼系數(shù)等參數(shù)可通過(guò)軟件靈活調(diào)整,甚至算法結(jié)構(gòu)也可重構(gòu),無(wú)需更改硬件。

- 易于集成與測(cè)試:整個(gè)鎖相環(huán)系統(tǒng)可集成于單顆FPGA芯片中,與數(shù)字信號(hào)處理、通信協(xié)議處理等其他功能模塊無(wú)縫集成,便于系統(tǒng)級(jí)設(shè)計(jì)與調(diào)試。

- 快速鎖定與強(qiáng)抗干擾能力:通過(guò)優(yōu)化數(shù)字環(huán)路濾波器算法,可以實(shí)現(xiàn)快速鎖定,并結(jié)合數(shù)字濾波技術(shù)有效抑制特定頻段的干擾。

其應(yīng)用領(lǐng)域廣泛:

- 通信系統(tǒng):用于載波同步、時(shí)鐘恢復(fù)、調(diào)制解調(diào)等,是軟件無(wú)線電和認(rèn)知無(wú)線電的關(guān)鍵技術(shù)。

- 電力電子:應(yīng)用于并網(wǎng)逆變器、有源電力濾波器的電網(wǎng)同步,實(shí)現(xiàn)單位功率因數(shù)運(yùn)行。

- 精密測(cè)量:在激光測(cè)距、原子鐘同步、矢量網(wǎng)絡(luò)分析儀等儀器中,用于產(chǎn)生高穩(wěn)定度的本振信號(hào)或進(jìn)行相位精確測(cè)量。

- 電機(jī)控制:用于無(wú)位置傳感器電機(jī)控制中的轉(zhuǎn)子位置與速度估算。

四、挑戰(zhàn)與展望

盡管優(yōu)勢(shì)明顯,該技術(shù)也面臨一些挑戰(zhàn),如高速高精度ADC與FPGA接口設(shè)計(jì)、數(shù)字量化噪聲與時(shí)鐘抖動(dòng)的抑制、復(fù)雜算法的實(shí)時(shí)實(shí)現(xiàn)與資源平衡等。隨著FPGA工藝的不斷進(jìn)步(如更小的制程、更快的SerDes接口、集成硬核處理器),以及高級(jí)綜合工具和基于模型的設(shè)計(jì)方法的發(fā)展,基于FPGA的數(shù)字化自動(dòng)鎖相技術(shù)將向著更高性能、更低功耗、更智能(如結(jié)合人工智能算法進(jìn)行參數(shù)自適應(yīng)優(yōu)化)和更易用的方向發(fā)展,在5G/6G通信、新能源發(fā)電、工業(yè)物聯(lián)網(wǎng)、航空航天等前沿領(lǐng)域發(fā)揮更為關(guān)鍵的作用。

基于現(xiàn)場(chǎng)可編程門陣列的數(shù)字化自動(dòng)鎖相技術(shù),融合了數(shù)字信號(hào)處理的靈活性與FPGA硬件的高效性,是實(shí)現(xiàn)高可靠、高性能相位同步與頻率合成的重要解決方案,具有深厚的理論研究?jī)r(jià)值和廣闊的工程應(yīng)用前景。